Summary

2025–2026 CRITICAL MATERIALS REPORT(CMR)

WAFER LEVEL METAL PLATING CHEMICALS

FOR FRONT END SEMICONDUCTOR MANUFACTURING AND ADVANCED PACKAGING APPLICATIONS

SUPPLY-CHAIN & MARKET ANALYSIS

This report covers the Metal Chemicals market trends and supply-chain as it applied to Advanced Packaging (wafer level) and Semiconductor Device Manufacturing (damascene process). Included are forecasts for copper plating and additives, market shares, technical trends, and supplier profiles. Also included in the appendix is a supplier product comparison table of publicly available information on plating products used for advanced packaging.

-

Provides strategic market and supply-chain analysis on metal plating chemicals used for semiconductor manufacturing including advanced packaging (wafer level) and semiconductor device manufacturing (damascene process) applications.

-

Covers information about forecasts for copper plating and additives, market shares, technical trends, and supplier profiles.

-

Includes 3 Quarterly Updates, with updates on market trends and forecasts from the analyst.

ページTOPに戻る

Table of Contents

1 EXECUTIVE SUMMARY 10

1.1 EXECUTIVE SUMMARY 11

1.2 ADVANCED PACKAGING PER WAFER STARTS 12

1.3 DEVICE DEMAND DRIVERS - LOGIC 13

1.4 CU PLATING FORECAST FOR CHIP INTERCONNECTS AND ADVANCED PACKAGING 14

1.5 MARKET SHARES ESTIMATES BASED ON ADDITIVES 15

1.6 SUPPLIER ACTIVITIES & VARIOUS ANNOUNCEMENTS 16

1.7 RISK FACTORS 17

1.8 ANALYST ASSESSMENT 18

2 SCOPE, PURPOSE AND METHODOLOGY 19

2.1 SCOPE, PURPOSE & METHODOLOGY 20

2.2 OVERVIEW OF TECHCET MATERIALS FOCUS AREAS 21

3 SEMICONDUCTOR INDUSTRY MARKET STATUS & OUTLOOK 22

3.1 WORLDWIDE ECONOMY AND OUTLOOK 23

3.2 WORLDWIDE ECONOMY AND OVERVIEW 24

3.2.1 WORLDWIDE ECONOMY AND SEMICONDUCTOR MARKET OVERVIEW 25

3.2.2 SEMICONDUCTOR INDUSTRIES TIES TO THE GLOBAL ECONOMY 26

3.2.3 TECHCET SEMICONDUCTOR SALES GROWTH OUTLOOK THROUGH 2029 27

3.2.4 TAIWAN OUTSOURCE MANUFACTURER MONTHLY SALES TRENDS 28

3.3 CHIPS SALES BY ELECTRONIC GOODS SEGMENT 29

3.3.1 FACTORS IMPACTING ELECTRONIC SYSTEMS OUTLOOK 30

3.3.2 PC OUTLOOK 31

3.3.3 SMARTPHONE OUTLOOK 32

3.3.4 AUTOMOTIVE INDUSTRY OUTLOOK 33

3.3.5 SERVERS / IT MARKET 36

3.4 SEMICONDUCTOR FABRICATION GROWTH & EXPANSION 39

3.4.1 IN THE MIDST OF HUGE INVESTMENT IN CHIP EXPANSIONS 40

3.4.2 PUBLIC FUNDS STIMULATING PRIVATE INVESTMENTS IN EXPANSION ACROSS THE GLOBE 41

3.4.3 SEMICONDUCTOR SUPPLY CHAIN ANNOUNCED EXPANSIONS IN THE US 42

3.4.4 TECHCET SEMICONDUCTOR EQUIPMENT MARKET FORECAST THROUGH 2029 43

3.4.5 TECHNOLOGY ROADMAPS 44

3.5 POLICY & TRADE TRENDS AND IMPACT 45

3.6 SEMICONDUCTOR PRODUCTION (WAFER STARTS*) AND MATERIALS OVERVIEW 47

3.6.1 TECHCET WAFER STARTS FORECAST THROUGH 2029 48

3.6.2 TECHCET ELECTRONIC MATERIALS MARKET FORECAST THROUGH 2029 49

4 METAL CHEMICALS MARKET BY SEGMENT 50

4.1 DEFINITIONS 51

4.2 METAL PLATING CHEMICALS MARKET OVERVIEW 53

4.2.1 OVERVIEW - CU ADVANCED PACKAGING AND CHIP INTERCONNECTS METALLIZATION 54

4.2.2 OVERVIEW - PLATING MARKET TRANSITIONAL TRENDS 55

4.3 ADVANCED PACKAGING METALLIZATION – MARKET DRIVERS 56

4.3.1 ADVANCED PACKAGING - ADDITIVES FOR CU PLATING REVENUE 57

4.3.2 ADVANCED PACKAGING – COPPER CHEMICALS REVENUE 58

4.3.3 ADVANCED PACKAGING ADDITIVE VOLUMES 59

4.3.4 INTERCONNECTS FOR ADVANCED PACKAGING 60

4.3.5 SN / SNAG PLATING 61

4.3.5.1 WW NI PLATING MARKET FORECAST 62

4.4 CHIP INTERCONNECTS GROWTH TRENDS 63

4.4.1 ADVANCED NODE CHIP INTERCONNECTS GROWTH DRIVERS 64

4.4.2 CHIP INTERCONNECTS CU PLATING REVENUES 65

4.4.3 CHIP INTERCONNECTS ADDITIVE VOLUMES 66

4.5 MINE LOCATIONS FOR METALS IN PLATING CHEMICALS 67

4.6 POSSIBLE CHOKE POINTS FOR METALS USED IN IC PLATING 68

4.7 FUTURE POSSIBLE DEMAND PRICE PRESSURES 69

5 TECHNICAL TRENDS 70

5.1 CHEMISTRIES USE FOR SEMICONDUCTOR METAL PLATING 71

5.2 PACKAGING TECH TRENDS 72

5.2.1 INTEGRATION IN ADVANCED PACKAGING VS. WAFER FABRICATION 73

5.2.2 ADVANCED PACKAGING DRIVERS 74

5.2.3 STATE OF THE ART EXAMPLES-COWOS(R), EMIB (R), AND RDL 75

5.2.4 PUSHING THE PACKAGING REQUIREMENTS AND STATE OF THE ART EXAMPLES-HBM 76

5.2.5 PACKAGING REQUIREMENTS AND STATE OF THE ART EXAMPLES-INTERPOSERS 77

5.2.6 PACKAGING REQUIREMENTS AND STATE OF THE ART EXAMPLES-PANEL PACKAGING 78

5.2.7 PACKAGING TECHNICAL CHALLENGES IN PLATING 79

5.3 TECHNICAL TRENDS WAFER INTERCONNECTS 80

5.3.1 MARKET DRIVES TECHNOLOGY TRENDS 81

5.3.2 ADVANCED LOGIC INTERCONNECT WIRING TECHNOLOGY EVOLUTION 82

5.3.2.1 TRENDS - MOL AND BEOL IRDS ROADMAP 83

5.3.3 CU CHIP INTERCONNECTS QUALIFICATION REQUIREMENTS 84

5.3.4 LOGIC METALLIZATION ROADMAP 85

5.3.4.1 INTERCONNECT FOR ADVANCED LOGIC 86

5.3.5 ADV LOGIC BURIED POWER RAIL 87

5.3.6 TECHNOLOGY ROADMAP: DRAM WITH MO OR RU 88

5.3.6.1 GENERAL PROCESS FLOW ADVANCED DRAM 89

5.3.7 PRECURSOR TECHNOLOGY ROADMAP: 3D NAND USING MO OR RU 90

5.3.7.1 3D-NAND GENERATIONS 2020 -2027 91

5.3.8 EXAMPLE OF LOGIC PROCESS FLOW 20 NM TO 32 NM LOGIC PVD 92

5.3.9 TECHNICAL REQUIREMENTS SUMMARY 1/2 93

5.3.9.1 TECHNICAL REQUIREMENTS SUMMARY 2/2 94

6 COMPETITIVE LANDSCAPE 95

6.1 TOTAL ADVANCED PACKAGING AND INTERCONNECTS MARKET SHARES 96

6.2 OEM MARKET SHARE – PLATING EQUIPMENT 97

6.3 MARKET SHARE BY APPLICATION – CU PLATING FOR ADVANCED PACKAGING 98

6.4 REGIONAL PLAYERS AND OTHERS 99

6.5 M&A ACTIVITY 100

7 ANALYST ASSESSMENT 101

7.1 ADVANCED METAL PLATING APPLICATIONS MARKET ASSESSMENT 102

8 SUPPLIER PROFILES 103

BASF

DUPONT

CHANG CHUN GROUP

INCHEON CHEMICAL COMPANY

ISHIHARA CHEMICAL/UNICON

AND MORE

9 APPENDIX A: PACKAGING TECH TRENDS 170

9.1 TECHNOLOGY CHALLENGE 171

9.1.1 METAL CLEANINGS CHALLENGE 172

9.1.2 MARKET DYNAMICS 173

9.1.3 WAFER LEVEL PLATING-FIRST LEVEL INTERCONNECT 174

9.1.4 MARKET DRIVERS OF ADVANCED PACKAGING APPLICATIONS 175

9.1.5 WAFER LEVEL PACKAGING ARCHITECTURES 176

9.1.6 TECH TRENDS - RDL 177

9.1.6.1 DAMASCENE-TYPE RDL 178

9.1.7 MARKET DRIVERS OF CHIPLET ARCHITECTURE 179

9.1.7.1 MARKET DRIVERS OF ADVANCED PACKAGING APPLICATIONS 180

9.1.7.2 INTERPOSERS (NOT WLPS) 181

9.1.8 TSV FILLING 2.5-3D 182

9.1.9 PACKAGING ELECTROPLATING REQUIREMENTS 183

9.1.9.1 PACKAGING ELECTROPLATING REQUIREMENTS - LISTING 184

ページTOPに戻る

List of Tables/Graphs

FIGURES

FIGURE 1.1: PLATING MATERIALS FOR ADVANCED PACKAGING AND INTERCONNECT REVENUES ($M’S) 11

FIGURE 1.2: WAFERS/YR & % OF PACKAGING THAT IS ADVANCED PACKAGING 12

FIGURE 1.3: ADVANCED LOGIC DEVICE GROWTH FORECAST 13

FIGURE 1.4: COPPER PLATING CHEMICALS REVENUES ($M’S) FOR ADVANCED PACKAGING & FE CU INTERCONNECTS 14

FIGURE 1.5: 2023 SUPPLIER MARKET SHARES CU PLATING FOR INTERCONNECT ADDITIVES 15

FIGURE 1.6: 2023 SUPPLIER MARKET SHARES CU PLATING FOR ADVANCED PACKAGING 15

FIGURE 3.1: HISTORICAL AND FORECASTED GDP GROWTH (2000 – 2029) 25

FIGURE 3.2: GLOBAL ECONOMY AND THE ELECTRONICS SUPPLY CHAIN 26

FIGURE 3.3: WORLDWIDE SEMICONDUCTOR SALES ($B) 27

FIGURE 3.4: TECHCET’S TAIWAN SEMICONDUCTOR INDUSTRY INDEX (TTSI) MOMENTUM TRACKER 28

FIGURE 3.5: 2024 SEMICONDUCTOR CHIP APPLICATIONS 29

FIGURE 3.6: SMARTPHONE SHIPMENTS, WW ESTIMATES 32

FIGURE 3.7: GLOBAL LIGHT VEHICLE PRODUCTION FORECAST 33

FIGURE 3.8: US EV RETAIL SHARE FORECAST 34

FIGURE 3.9: AUTOMOTIVE SEMICONDUCTOR FORECAST ESTIMATES 35

FIGURE 3.10: AI VALUE FORECAST ($B’S USD) 37

FIGURE 3.11: SCALE OF TODAY’S AI-CENTRIC DATA CENTERS 38

FIGURE 3.12: TSMC PHOENIX FAB INVESTMENT TO EXCEED US $65B 39

FIGURE 3.13: ESTIMATED GLOBAL FAB INVESTMENT 2024-2029 40

FIGURE 3.14: ANNOUNCED PUBLIC STIMULUS AND RESPECTIVE SEMICONDUCTOR CHIP MANUFACTURING REGIONS 41

FIGURE 3.15: SEMICONDUCTOR SUPPLY CHAIN EXPANSIONS WITHIN THE US 42

FIGURE 3.16: TECHCET WORLDWIDE SEMICONDUCTOR EQUIPMENT FORECAST 43

FIGURE 3:17: TSMC LOGIC ROADMAP BY NODE 44

FIGURE 3.18: TECHCET WAFER START FORECAST BY NODE SEGMENTS 48

FIGURE 3.19: TECHCET WORLDWIDE ELECTRONIC MATERIALS FORECAST 49

FIGURE 4.1: PACKAGING METALLIZATION APPLICATIONS 51

FIGURE 4.2: USE OF SILICON INTERPOSER IN 2.5D PACKAGING 52

FIGURE 4.3: VERSIONS OF TSV & PROCESS FLOW EXAMPLE 53

FIGURE 4.4: PLATING MATERIALS FOR ADVANCED PACKAGING AND INTERCONNECT REVENUES 53

FIGURE 4.5: CU PLATING CHEMICALS 5-YEAR FORECAST 54

FIGURE 4.6: WAFERS/YR & % OF PACKAGING THAT IS ADVANCED PACKAGING (AP) 56

FIGURE 4.7: REVENUE FORECAST CU PLATING ADVANCED PACKAGING 57

FIGURE 4.8: CU PILLAR & CU RDL SEGMENTED FORECAST 58

FIGURE 4.9: ADV. PACKAGING CU CUSO4 AMOUNT DEMAND FORECAST 59

FIGURE 4.10: ADV. PACKAGING CU/VMS VOLUME DEMAND FORECAST ADV. PACKAGING CU PLATING ADDITIVES 59

FIGURE 4.11: BUMPING MATERIALS FOR FIRST LEVEL INTERCONNECT 60

FIGURE 4.12: HYBRID BONDING PROCESS 60

FIGURE 4.13: SN AND SNAG PLATING REVENUE 61

FIGURE 4.14: NICKEL PLATING REVENUE 62

FIGURE 4.15: ADVANCED LOGIC DEVICE GROWTH FORECAST 63

FIGURE 4.16: METAL PLATING WAFER PASSES 64

FIGURE 4.17: WW DAMASCENE REVENUE FORECAST ESTIMATES 65

FIGURE 4.18: DAMASCENE CUSO4 VOLUME DEMAND FORECAST 66

FIGURE 4.19: DAMASCENE CU PLATING CHEMICAL AMOUNT DEMAND FORECAST 66

FIGURE 5.1: KEY TRENDS IN ADVANCED PACKAGING 72

FIGURE 5.2: COST AND COMPLEXITY OF SOC AND CHIPLET 73

FIGURE 5.3: I/O DENSITY DRIVES PACKAGING EVOLUTION 74

FIGURE 5.4: INTEGRATION ARCHITECTURES FOR 2.5D PACKAGING 75

FIGURE 5.5: SEM IMAGE OF 2.5D PACKAGE 75

FIGURE 5.6: SEM IMAGE OF EMBEDDED DIE FROM INTEL 75

FIGURE 5.7: HIGH BANDWIDTH MEMORY STACKING 76

FIGURE 5.8: INCREASING HBM COUNT DRIVES NEW TECHNOLOGIES ABOVE 3.3 RETICLE 77

FIGURE 5.9: COMPARISON OF WAFER AND PANEL FORMATS USED IN PACKAGING 78

FIGURE 5.10: CHALLENGES OF ELECTROPLATING VIA FILL 79

FIGURE 5.11: METAL INTERCONNECTS BY LOGIC NODE 81

FIGURE 5.12: INTERCONNECT METAL COMPARISON BY RESISTIVITY 82

FIGURE 5.13: CU CHIP INTERCONNECTS QUALIFICATION 84

FIGURE 5.14: LEADING EDGE LOGIC POWER RAIL SCHEMES 87

FIGURE 5.15: DRAM STRUCTURE 88

FIGURE 5.16: 3D NAND STRUCTURE 90

FIGURE 5.17: HVM 3D NAND ROADMAP, INCLUDING RISK STARTS 91

FIGURE 6.1: TOTAL PLATING FOR ADVANCED PACKAGING AND CU INTERCONNECT ADDITIVES 2023 96

FIGURE 6.2: PLATING EQUIPMENT OEM MARKET SHARES % 2023 97

FIGURE 6.3: CU PLATING VOLUME BY REGION 98

FIGURE 9.1: CLEANING COMPLEXITY 171

FIGURE 9.2: OSATS PACKAGING BUSINESS CANNIBALIZATION TREND 173

FIGURE 9.3: INTERCONNECT BONDING METHODS 174

FIGURE 9.4: WAFER LEVEL PLATING 174

FIGURE 9.4: ADVANCED PACKAGING MARKET DRIVERS AND APPLICATIONS 175

FIGURE 9.5: FAN-IN (WLCSP) & FAN-OUT (WLFO) COMPARISON 176

FIGURE 9.6: RDL CIRCUITRY EXAMPLE 177

FIGURE 9.7: COMPARISON WITH DAMASCENE- TYPE RDL 178

FIGURE 9.8: COST/PERFORMANCE IMPROVEMENTS THROUGH CHIPLETS INTEGRATION 179

FIGURE 9.9: 2.5 AND 3D PACKAGING EXAMPLES 180

FIGURE 9.10: USE OF SILICON INTERPOSER 181

FIGURE 9.11: TSV PROCESS FLOW EXAMPLE 182

FIGURE 9.12: PROCESS COMPARISON OF TRADITIONAL VS. WLP FLOWS 183

TABLES

TABLE 3.1: GLOBAL GDP AND SEMICONDUCTOR REVENUES 23

TABLE 3.2: INITIALLY ANNOUNCED* US RECIPROCAL TARIFF SCHEDULE 24

TABLE 3.3: WORLDWIDE PC FORECAST BY SEGMENT 31

TABLE 3.4: IT MARKET SPENDING FORECAST, 2025 36

TABLE 5.1: IRDS 2023 MORE MOORE INTERCONNECT ROADMAP 82

TABLE 5.2: BARRIER METAL ROADMAP 85

TABLE 5.3: METALS REQUIRED FOR DEVICE FEATURES 86

TABLE 5.4: DRAM USE OF MO OR RU PRESENT & FUTURE 88

TABLE 5.5: GENERAL PROCESS FLOW ADVANCED DRAM 89

TABLE 5.6: 3D NAND MATERIAL CHANGES PRESENT & FUTURE 90

TABLE 5.7: EXAMPLE OF LOGIC PROCESS FLOW 20 NM TO 32 NM LOGIC PVD 92

TABLE 5.8: TECHNICAL REQUIREMENTS SUMMARY 93

TABLE 5.9: TECHNICAL REQUIREMENTS SUMMARY, CONTINUED 94

TABLE 6.1: REGIONAL PLAYERS – MARKET LEADER AND “OTHERS” 99

TABLE 9.1: CU PACKAGING APPLICATIONS AND REQUIREMENTS 84

Press Release

November 24, 2025 | Press Release

Rising Copper Plating Demand in Semiconductors Driven by Advanced Packaging and FE Interconnects

San Diego, CA, :

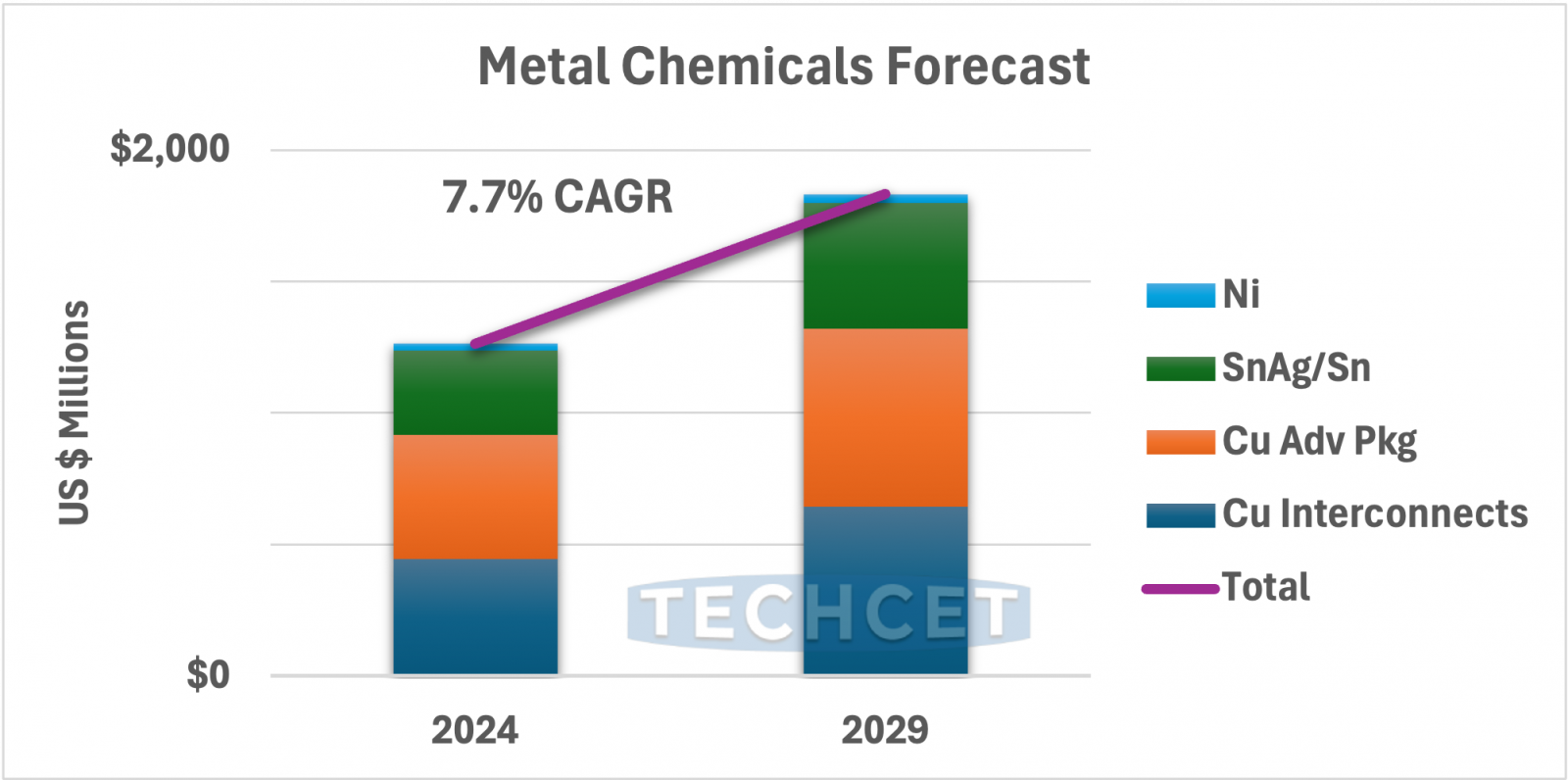

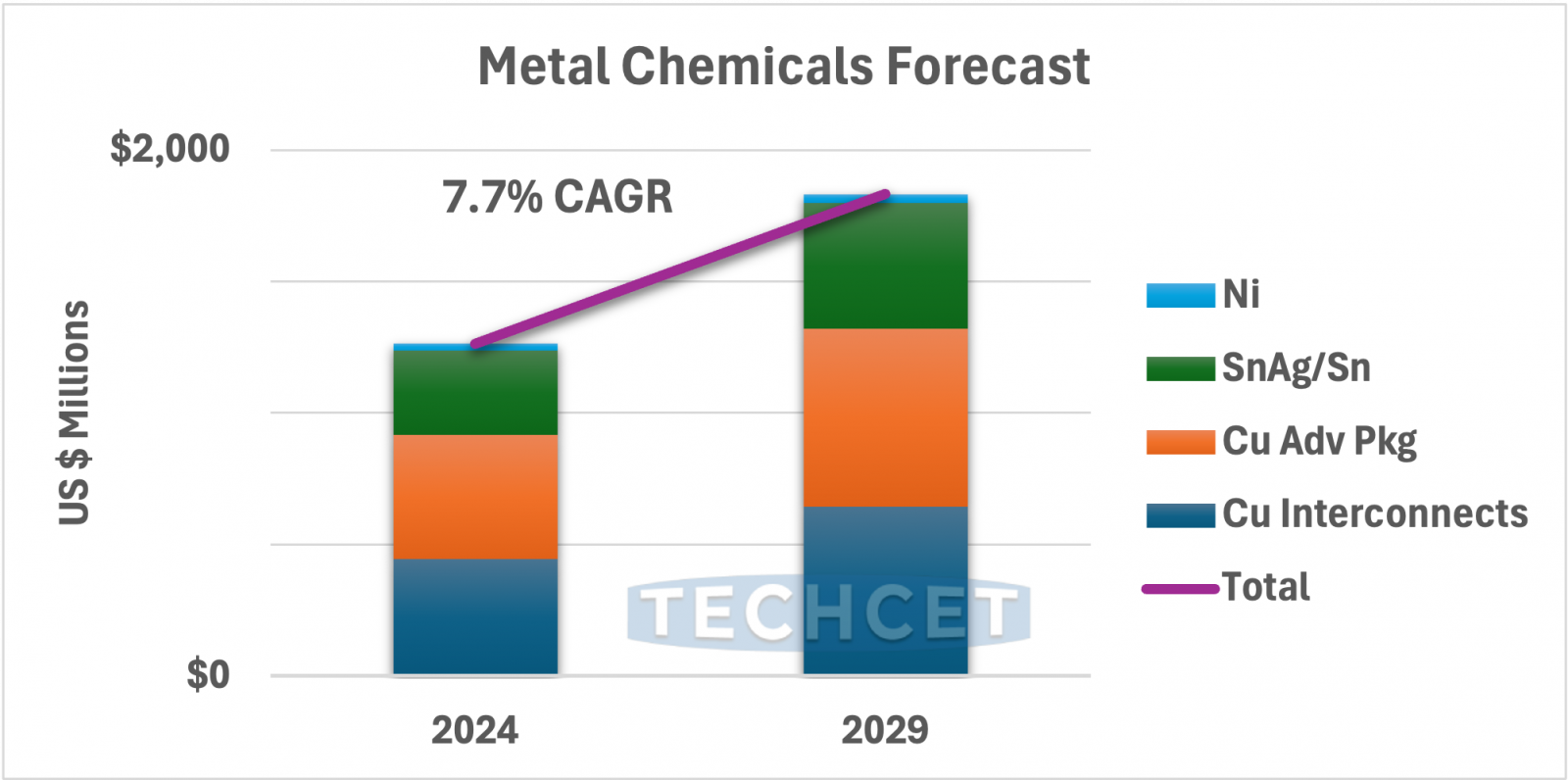

TECHCET, the global plating chemicals market is projected to reach US$1,381M in 2025, up 9.3% from 2024. Copper leads the market, split between US$495M for device interconnects and US$509M for advanced packaging in 2025. The advanced laminate substrates applications currently see the bulk of demand within the packaging segment. But this is expected to shift as more plating and CMP are required to support larger interposers, panel level packaging and hybrid bonding, now starting to emerge. Growth is fueled by rising interconnect densities in advanced logic, demand from HPC and AI, and increasing adoption of advanced packaging according to TECHCET’s 2025-2026 Critical Materials Report(TM) on Metal Chemicals.

Metal Chemicals Forecast 2024-2029

Industry momentum is reinforced by major investments: MacDermid Alpha launched MICROFAB SC-40 PLUS for Cu pillar plating; MKS/Atotech is building a $40M chemicals plant in Thailand; and Moses Lake Industries opened a $100M Arizona R&D facility for high-purity electrolytes and Cu plating. Meanwhile, TSMC, Amkor, and ASE are expanding U.S. packaging capacity to support demand from AI, datacenter, and automotive markets.

The Metal Chemicals report specifically covers copper (Cu) pillar, micro-bump (µBump), wafer-level packaging (WLP), redistribution layers (RDL), and through-silicon-via (TSV), with updated modeling that more accurately reflects Cu content in packaging, driving higher forecasts for both volume and revenue.